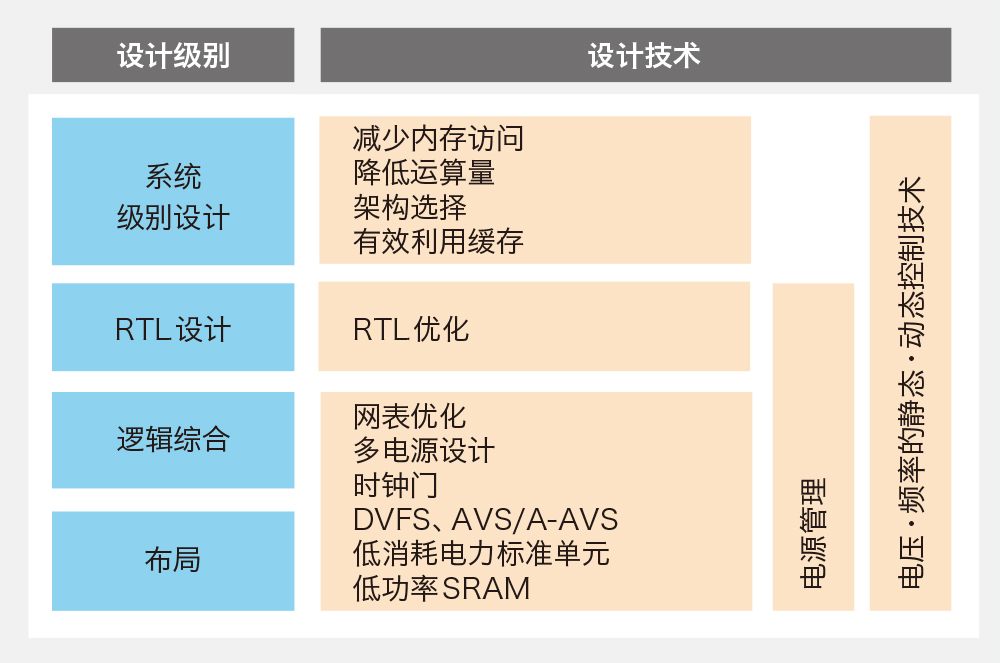

[低消耗电力化技术]

近年来,降低LSI功耗的需求越来越高。本公司的SoC设计,为了满足客户对低功耗的需求,采取了各种措施。为了实现低功耗LSI,不能仅靠个别技术,而是须要综合各种技术才会有效。在本公司的设计环境“参考设计流程”中,支持各种低功耗技术, LSI运作时和待机时均可以降低功耗。特别是针对以控制电源方式实现低功耗化的手法进行了体系化的开发。另外本公司通过全面采用UPF/CPF,减少对客户资产的设计变更,使低功耗设计变得更加容易。并且通过采用UPF/CPF,对过去验证难度很高的低功耗技术也能进行高可靠性设计。

多电源设计

[多电源设计技术]

通过在LSI内供给不同电压的技术,对高速运行的电路模块提供高电压,对低速运行的电路块提供低电压,降低运行时的耗电量。

通过采用UPF/CPF,使不同电压的电路模块可以进行一次性物理设计·验证,通过这种方式可以最大程度减少由于低耗电设计引起的开发周期的增加。

通过采用UPF/CPF,使不同电压的电路模块可以进行一次性物理设计·验证,通过这种方式可以最大程度减少由于低耗电设计引起的开发周期的增加。

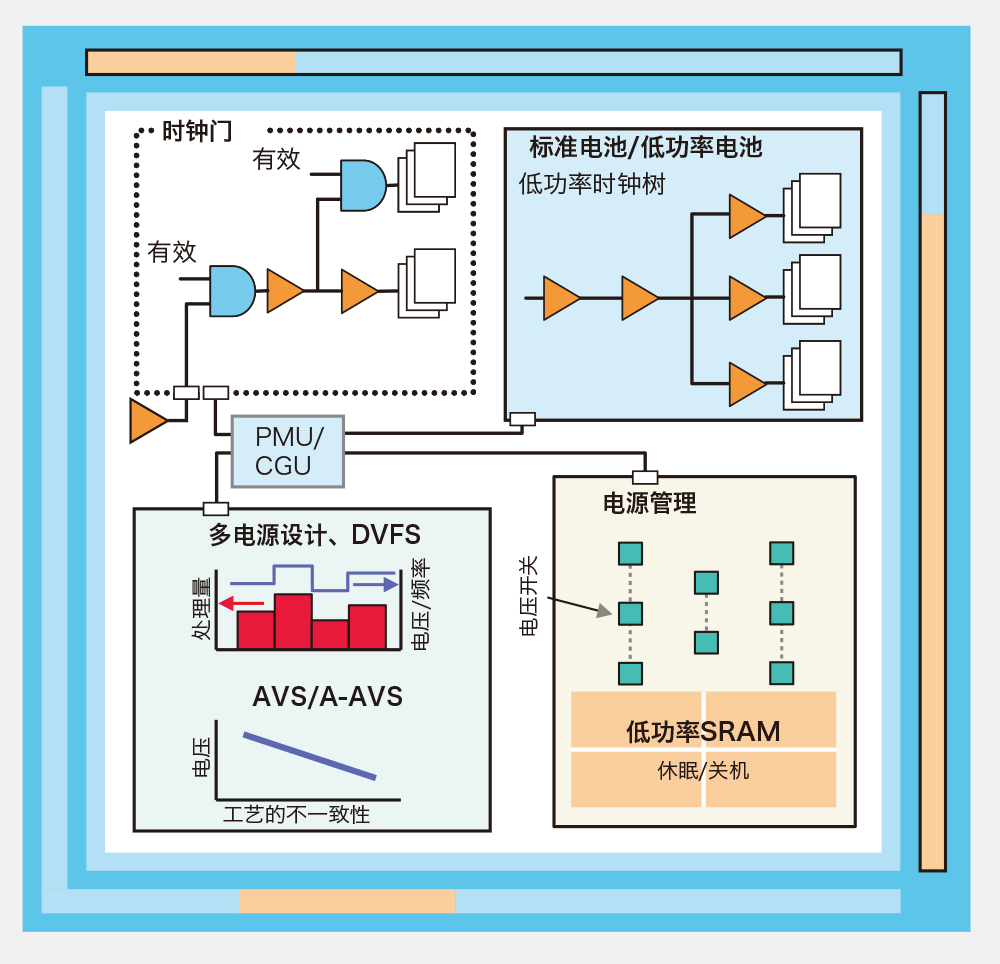

时钟门

通过停止不运行的电路模块的时钟,可降低LSI运行时的耗电总量。

电源管理

提供统一电力门控和SRAM睡眠、关机模式的电源管理。彻底排除损耗,提高低功耗化。

本公司电源管理技术,采用独创的电源开关控制方式,抑制了供电开关切换时产生的电源噪声,避免LSI的误运行。

而且通过采用UPF/CPF,包括电源切断电路模块,可以一并进行性物理设计·验证,尽量抑制开发周期的增加。

本公司电源管理技术,采用独创的电源开关控制方式,抑制了供电开关切换时产生的电源噪声,避免LSI的误运行。

而且通过采用UPF/CPF,包括电源切断电路模块,可以一并进行性物理设计·验证,尽量抑制开发周期的增加。

适应性电源控制(DVFS*1、AVS*2/Advanced-AVS)

支持根据需求处理量改变电压和频率的DVFS。同时根据制造偏差确定相应的运行电压,通过在保证LSI运行的最低电压下运行,可降低运行时和待机时的耗电。

*1:DVFS(Dynamic Voltage Frequency Scaling)

*2:AVS(Adaptive Voltage Scaling)

*1:DVFS(Dynamic Voltage Frequency Scaling)

*2:AVS(Adaptive Voltage Scaling)

标准单元

采用最先进的技术,不仅是标准单元的面积,布线性也对LSI低功耗化做出贡献。我们提供本公司独创设计的凌驾于其他公司产品的标准单元。

还扩充了对时钟系的低功耗化有效的单元的阵容。

还扩充了对时钟系的低功耗化有效的单元的阵容。

低功率SRAM

搭载了大容量SRAM的LSI可能会出现SRAM的耗电问题。在这种情况下,通过使用多模式SRAM可降低耗电量。在多模式SRAM,除了通常运行模式外,还有待机模式、休眠模式和关机模式。在待机模式,通过停止SRAM宏内部的时钟运行,可使SRAM宏的动态电为0。在休眠模式,通过将SRAM宏的周边电路置于非激活状态,可降低漏电。在关机模式可通过SRAM独立切断电源。另外使用SRAM结构优化也有助于低功耗化。从逻辑设计阶段开始支持客户选择最佳的SRAM。

| 运行方式 | 功能 | 效果 |

|---|---|---|

| 通常运行 | 通常的RAM运行 | - |

| 备用 | 运行停止 | 运行功率为0 |

| 休眠 | 数据保存 | 漏电约为1/3* |

| 关机 | SRAM独立切断电源 | 漏电约为1/6* |

*:取决于SRAM配置

全面采用UPF/CPF的低功耗设计环境

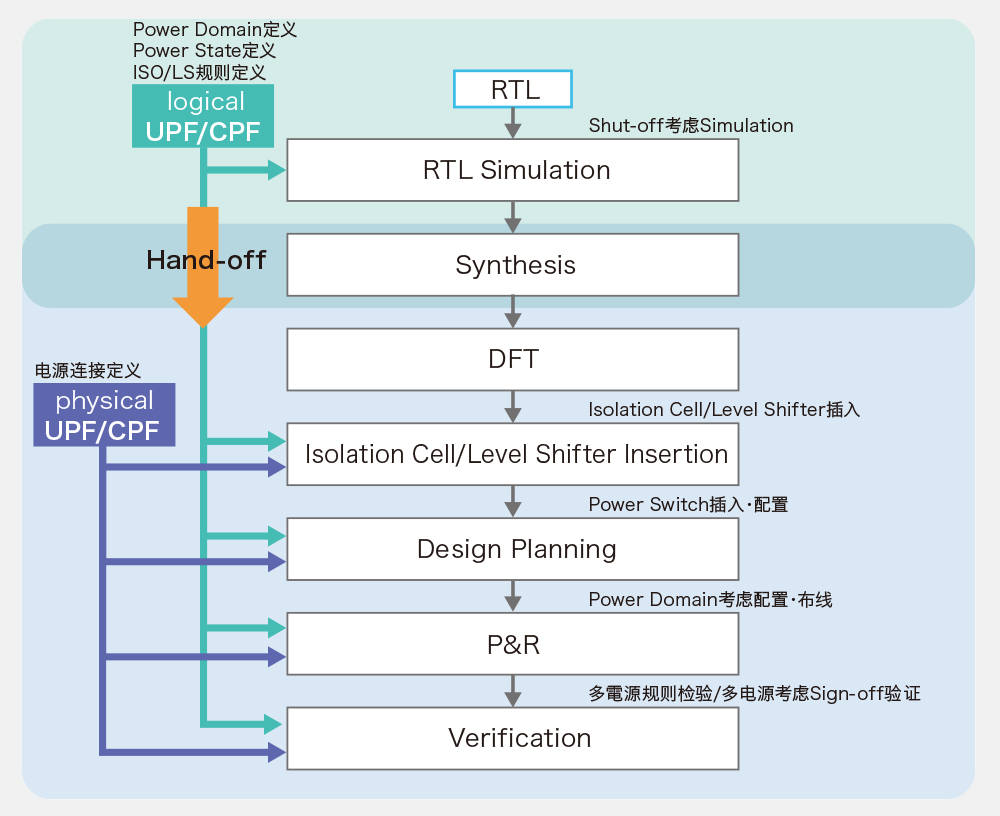

本公司通过UPF*1及CPF*2对电源规格进行一贯管理,支持电力门控设计和多电源・多电压设计,针对IP的增加使电源设计变得更加复杂,我们进行RTL仿真、多电源验证及物理设计,提供整体解决方案。这个解决方案把电源规格分为逻辑规格和物理规格管理,通过定义逻辑规格,可进行RTL仿真的切断电源验证。把验证的RTL和电源逻辑规格切换为物理设计,备有定义电源连接的电源的物理规格,基于这些电源规格(UPF/CPF)进行物理设计。按上述方式电源规格通过UPF/CPF进行管理,通过设计流程使用,明确电源规格,可进行高可靠性设计。

*1:UPF(Unified Power Format)是用来描述作为IEEE Std. 1801IEEE Std. 1801标准化的低功耗设计指针的标准规格 (http://www.ieee.org/)。

*2:CPF(Common Power Format) 是用来描述已在Si 2标准化的低功耗设计指南的标准规格 (http://www.si2.org/?page=811)。

*1:UPF(Unified Power Format)是用来描述作为IEEE Std. 1801IEEE Std. 1801标准化的低功耗设计指针的标准规格 (http://www.ieee.org/)。

*2:CPF(Common Power Format) 是用来描述已在Si 2标准化的低功耗设计指南的标准规格 (http://www.si2.org/?page=811)。

[全面采用UPF/CPF的低功耗设计环境]